Bus I2C — gán, thiết bị, truyền dữ liệu, đánh địa chỉ

Khi tạo một mạch điện tử, nhiều nhà phát triển phải đối mặt với nhu cầu sử dụng một số lượng lớn chip trung gian để khớp, lấy mẫu và xử lý các khối riêng lẻ của nó. Để giảm thiểu số lượng chip phụ trợ, Philips đã đề xuất giao diện mạng nối tiếp I2C hai chiều hai dây từ những năm 1980, được thiết kế đặc biệt để quản lý nhiều chip trong một thiết bị.

Ngày nay, riêng Philips đã sản xuất hơn một trăm thiết bị tương thích I2C cho thiết bị điện tử với nhiều mục đích khác nhau: bộ nhớ, hệ thống xử lý video, bộ chuyển đổi tương tự sang kỹ thuật số và kỹ thuật số sang tương tự, trình điều khiển hiển thị, v.v.

Bus I2C là một sửa đổi của giao thức trao đổi dữ liệu nối tiếp có khả năng truyền dữ liệu 8 bit nối tiếp ở chế độ "nhanh" thông thường với tốc độ từ 100 đến 400 kbps. Quá trình trao đổi dữ liệu được thực hiện ở đây chỉ trên hai dây (không tính dây chung): đường SDA dành cho dữ liệu và đường SCL để đồng bộ hóa.

Xe buýt trở thành hai chiều do thực tế là các tầng đầu ra của thiết bị được kết nối với xe buýt có các bộ thu hoặc kênh mở, do đó sao chép hệ thống dây AND. Kết quả là, bus giảm thiểu số lượng kết nối giữa các chip, để lại ít chân và dấu vết cần thiết hơn trên bảng. Do đó, bản thân bảng trở nên đơn giản hơn, nhỏ gọn hơn và công nghệ tiên tiến hơn trong sản xuất.

Giao thức này cho phép bạn tắt bộ giải mã địa chỉ và logic đàm phán bên ngoài khác. Số lượng chip có thể hoạt động đồng thời trên bus I2C bị giới hạn bởi công suất của nó — tối đa là 400 pF.

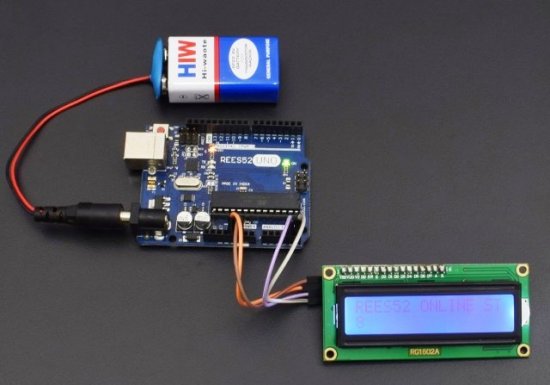

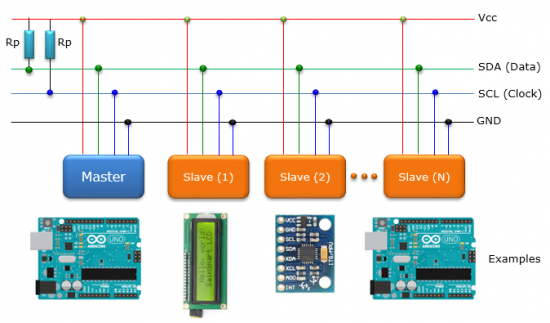

IC tương thích với I2C có thuật toán khử nhiễu phần cứng để đảm bảo tính toàn vẹn của dữ liệu ngay cả khi có nhiễu mạnh. Những thiết bị như vậy có giao diện cho phép các vi mạch giao tiếp với nhau ngay cả khi điện áp cung cấp của chúng khác nhau. Trong hình dưới đây, bạn có thể tự làm quen với nguyên tắc kết nối một số vi mạch thông qua một bus chung.

Mỗi thiết bị được kết nối với xe buýt có địa chỉ duy nhất của riêng nó, nó được xác định bởi nó và theo mục đích của thiết bị, nó có thể hoạt động như một máy thu hoặc máy phát. Khi truyền dữ liệu, các thiết bị này có thể là chủ (master) hoặc phụ (slave). Master là thiết bị bắt đầu truyền dữ liệu và tạo tín hiệu đồng hồ trên đường SCL. Slave, liên quan đến master, là thiết bị đích.

Tại bất kỳ thời điểm hoạt động nào trên bus I2C, chỉ một thiết bị có thể đóng vai trò là chủ; nó tạo ra tín hiệu trên đường SCL.Master có thể là máy thu chính hoặc máy phát chính.

Về nguyên tắc, xe buýt cho phép một số chủ khác nhau, nhưng áp đặt các hạn chế đối với các đặc điểm hình thành tín hiệu điều khiển và giám sát trạng thái của xe buýt; điều này có nghĩa là một số chủ có thể bắt đầu truyền cùng một lúc, nhưng các xung đột kiểu này được loại bỏ nhờ phân xử, nghĩa là cách chủ xử lý khi phát hiện ra rằng xe buýt đang bị chủ khác chiếm giữ.

Việc đồng bộ hóa một cặp thiết bị được đảm bảo bởi thực tế là tất cả các thiết bị được kết nối với xe buýt, tạo thành hệ thống dây "VÀ". Ban đầu, tín hiệu SDA và SCL ở mức cao.

BẮT ĐẦU và DỪNG

Quá trình trao đổi bắt đầu với việc tổng thể tạo trạng thái «BẮT ĐẦU»: trên đường SDA, tín hiệu chuyển từ trạng thái cao xuống thấp, trong khi đường SCL có mức cao ổn định. Tất cả các thiết bị được kết nối với xe buýt coi tình huống này là lệnh để bắt đầu trao đổi.

Mỗi chủ tạo ra một tín hiệu đồng hồ riêng trên đường SCL khi truyền dữ liệu trên xe buýt.

Quá trình trao đổi kết thúc với sự hình thành trạng thái STOP của chủ: trên đường SDA, tín hiệu thay đổi từ thấp lên cao, trong khi đường SCL có mức cao ổn định.

Trình điều khiển luôn đóng vai trò là nguồn tín hiệu START và STOP. Ngay khi tín hiệu «BẮT ĐẦU» được cố định, điều đó có nghĩa là đường dây đang bận. Đường dây miễn phí khi phát hiện thấy tín hiệu STOP.

Ngay sau khi khai báo trạng thái START, master sẽ chuyển dòng SCL xuống mức thấp và gửi bit quan trọng nhất của byte thông báo đầu tiên tới dòng SDA. Số lượng byte trong một tin nhắn không bị giới hạn.Các thay đổi trên đường SDA chỉ được kích hoạt khi mức tín hiệu trên đường SCL ở mức thấp. Dữ liệu hợp lệ và không nên thay đổi chỉ khi xung đồng bộ cao.

Xác nhận rằng byte từ máy phát chính đã được nhận bởi máy thu phụ được thực hiện bằng cách đặt một bit xác nhận đặc biệt trên dòng SDA sau khi nhận được bit dữ liệu thứ tám.

SỰ XÁC NHẬN

Vì vậy, việc gửi 8 bit dữ liệu từ máy phát đến máy thu kết thúc bằng một xung bổ sung trên đường SCL khi thiết bị nhận ở mức thấp trên đường SDA, cho biết rằng nó đã nhận được toàn bộ byte.

Xác nhận là một phần không thể thiếu trong quá trình truyền dữ liệu. Master tạo xung đồng bộ. Máy phát gửi trạng thái thấp tới SDA trong khi đồng hồ xác nhận đang hoạt động. Trong khi xung đồng bộ cao, máy thu phải giữ SDA ở mức thấp.

Nếu Slave đích không xác nhận địa chỉ của nó, ví dụ vì nó hiện đang bận, thì đường dữ liệu phải được giữ ở mức cao. Sau đó, thuyền trưởng có thể đưa ra tín hiệu DỪNG để hủy bỏ việc gửi đi.

Nếu việc nhận được thực hiện bởi máy thu chính, thì nó có nghĩa vụ thông báo cho máy phát phụ sau khi hoàn thành việc truyền - không phải bằng cách xác nhận byte cuối cùng. Bộ phát phụ giải phóng đường dữ liệu để chủ có thể phát tín hiệu DỪNG hoặc tín hiệu BẮT ĐẦU lặp lại.

Việc đồng bộ hóa các thiết bị được đảm bảo bởi thực tế là các kết nối với dòng SCL được thực hiện theo nguyên tắc "VÀ".

Master không có quyền duy nhất để kiểm soát quá trình chuyển đổi của dòng SCL từ thấp lên cao.Nếu nô lệ cần thêm thời gian để xử lý bit đã nhận, nó có thể giữ SCL ở mức thấp một cách độc lập cho đến khi sẵn sàng nhận bit dữ liệu tiếp theo. Dòng SCL trong tình huống như vậy sẽ ở mức thấp trong khoảng thời gian xung đồng bộ mức thấp dài nhất.

Các thiết bị có mức thấp duy trì thấp nhất sẽ không hoạt động cho đến khi thời gian dài kết thúc. Khi tất cả các thiết bị kết thúc giai đoạn đồng bộ thấp, SCL sẽ tăng cao.

Tất cả các thiết bị sẽ bắt đầu chạy ở mức cao và thiết bị đầu tiên hoàn thành chu kỳ của nó sẽ là thiết bị đầu tiên đặt dòng SCL ở mức thấp. Do đó, thời lượng của trạng thái thấp của SCL sẽ được xác định bởi trạng thái thấp dài nhất của xung đồng bộ hóa của một trong các thiết bị và thời lượng của trạng thái cao sẽ được xác định bởi khoảng thời gian đồng bộ hóa ngắn nhất của một trong các thiết bị. thiết bị.

Các tín hiệu đồng bộ hóa có thể được sử dụng bởi các máy thu như một phương tiện để kiểm soát việc truyền dữ liệu ở cấp độ bit và byte.

Nếu thiết bị có khả năng nhận byte ở tốc độ cao, nhưng phải mất một khoảng thời gian nhất định để lưu trữ byte đã nhận hoặc chuẩn bị nhận byte tiếp theo, thiết bị có thể tiếp tục giữ SCL ở mức thấp sau khi nhận và xác nhận một byte, buộc máy phát vào trạng thái chờ.

Một bộ vi điều khiển không có mạch phần cứng tích hợp, ví dụ như ở mức bit, có thể làm chậm tốc độ xung nhịp bằng cách tăng thời lượng ở trạng thái thấp của chúng.Kết quả là, tốc độ truyền của thiết bị chính sẽ được xác định bởi tốc độ của thiết bị chậm hơn.

ĐỊA CHỈ

Mỗi thiết bị được kết nối với bus I2C có một địa chỉ chương trình duy nhất mà chủ địa chỉ địa chỉ đó bằng cách gửi một lệnh cụ thể. Các vi mạch cùng loại được đặc trưng bởi một bộ chọn địa chỉ, được triển khai ở dạng đầu vào kỹ thuật số của bộ chọn hoặc ở dạng tương tự. Địa chỉ được chia thành không gian địa chỉ của các thiết bị được kết nối với xe buýt.

Chế độ bình thường giả định địa chỉ bảy bit. Việc đánh địa chỉ hoạt động như sau: sau lệnh «BẮT ĐẦU», chủ gửi byte đầu tiên, byte này xác định thiết bị nô lệ nào là cần thiết để giao tiếp với chủ. Ngoài ra còn có một địa chỉ cuộc gọi chung xác định tất cả các thiết bị trên xe buýt, tất cả các thiết bị (về mặt lý thuyết) đều phản hồi nó bằng một xác nhận, nhưng trong thực tế, điều này rất hiếm.

Vì vậy, bảy bit đầu tiên của byte đầu tiên là địa chỉ nô lệ. Bit ít quan trọng nhất, bit thứ tám, cho biết hướng gửi dữ liệu. Nếu có «0», thì thông tin sẽ được ghi từ chủ đến nô lệ này. Nếu «1», thông tin sẽ được đọc bởi chủ từ nô lệ này.

Sau khi chủ hoàn thành việc gửi byte địa chỉ, mỗi nô lệ sẽ so sánh địa chỉ của nó với nó. Bất kỳ ai có cùng địa chỉ đều là nô lệ và được xác định là người phát nô lệ hoặc người nhận nô lệ, tùy thuộc vào giá trị của bit có ý nghĩa nhỏ nhất của byte địa chỉ.

Một địa chỉ nô lệ có thể bao gồm các phần cố định và có thể lập trình. Thông thường, một số lượng lớn thiết bị cùng loại hoạt động trong một hệ thống, sau đó phần địa chỉ có thể lập trình cho phép sử dụng tối đa cùng loại thiết bị trên xe buýt. Có bao nhiêu bit trong byte địa chỉ có thể lập trình được tùy thuộc vào số lượng chân trống trên chip.

Đôi khi, một chân có cài đặt tương tự của dải địa chỉ có thể lập trình là đủ, chẳng hạn như SAA1064 - trình điều khiển chỉ báo LED có cách triển khai chính xác như vậy. Tiềm năng của một chân cụ thể xác định độ lệch của không gian địa chỉ của chip để các chip cùng loại không xung đột hoạt động trên cùng một bus. Tất cả các chip hỗ trợ bus I2C đều chứa một bộ địa chỉ mà nhà sản xuất chỉ định trong tài liệu.

Tổ hợp «11110XX» được dành riêng cho địa chỉ 10 bit. Nếu chúng ta tưởng tượng việc trao đổi dữ liệu từ lệnh «START» sang lệnh «STOP», nó sẽ như sau:

Các định dạng trao đổi dữ liệu đơn giản và kết hợp được phép ở đây. Định dạng kết hợp có nghĩa là giữa «START» và «STOP», master và Slave có thể đóng vai trò là bộ thu và bộ phát, điều này rất hữu ích, chẳng hạn như trong quản lý bộ nhớ nối tiếp.

Để byte dữ liệu đầu tiên truyền một địa chỉ bộ nhớ. Sau đó, lặp lại lệnh «BẮT ĐẦU» và đọc địa chỉ nô lệ, dữ liệu bộ nhớ sẽ hoạt động. Các quyết định tự động tăng hoặc giảm địa chỉ đã truy cập trước đó do nhà phát triển thiết bị đưa ra sau khi đã nghiên cứu tài liệu về chip trước đó. Bằng cách này hay cách khác, sau khi nhận được lệnh START, tất cả các thiết bị phải khôi phục logic của chúng và chuẩn bị cho thực tế là địa chỉ sẽ được đặt tên.